伯克利乱序执行RISC-V处理器(The Berkeley Out-of-Order RISC-V Processor)。

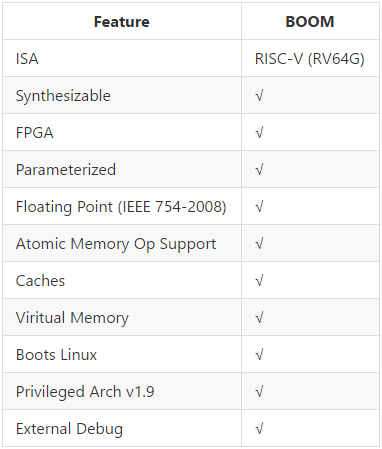

riscv-boom 是用Chisel硬件构造语言编写的RV64G RISC-V超标量Berkeley乱序机(BOOM)的源存储库。 BOOM是一个可合成的核心,目标ASIC过程。 它可以在FPGA(zc706上为50 MHz)上运行,但是将其优化为FPGA软核是一个非目标。

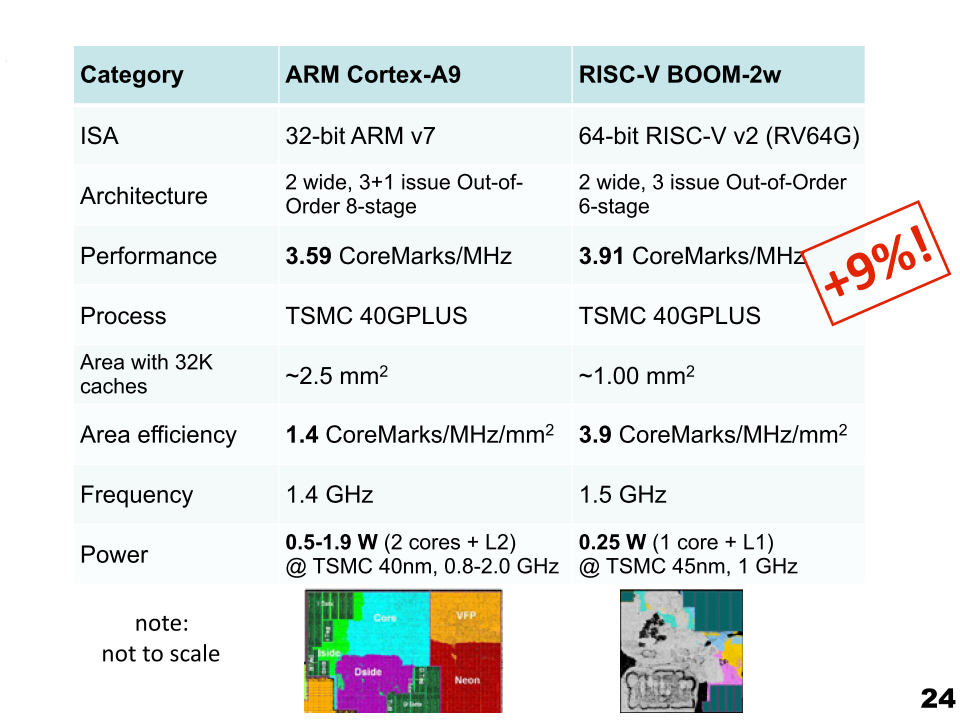

RISC-V BOOM(45nm)与ARM Cortex A9(40nm)在台积电(TSMC)的40/45纳米工艺下对比胜于A9。

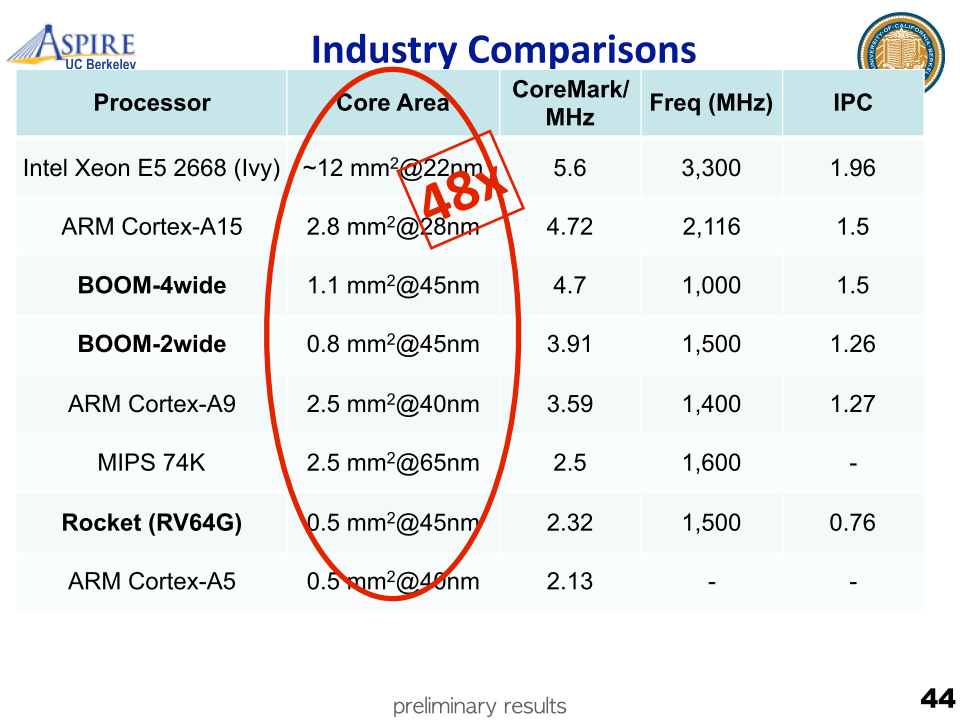

与其它工业产品对比优势依然。

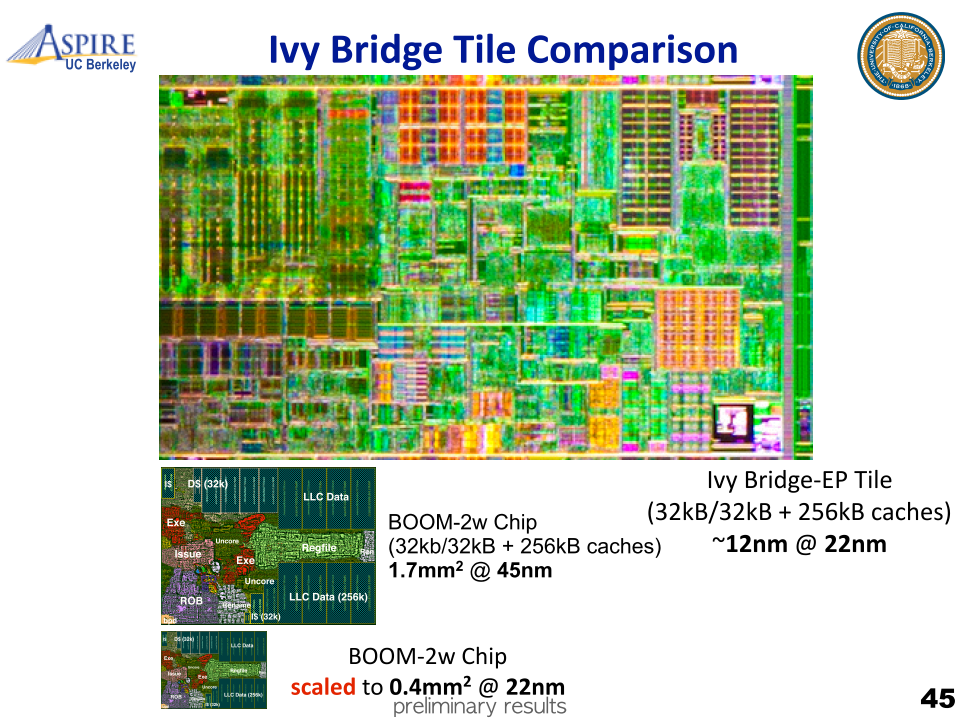

芯片面积对比